Ascend910系列:修订间差异

跳到导航

跳到搜索

无编辑摘要 |

无编辑摘要 |

||

| 第5行: | 第5行: | ||

Main features: | Main features: | ||

# | # The Huawei Ascend 910 has 32 DaVinci AI cores. | ||

# | # The chip combines these DaVinci AI cores with high-speed HBM2 memory. | ||

# | # The main chip also has additional logic blocks such as 128 channel video decoding engines. | ||

# | # There is a Nimbus V3 chip that handles most of the I/O and is co-packaged alongside the main chip and the HBM2 stacks. | ||

# | # The Huawei Ascend 910 is designed to run at a higher power envelope (350W) and higher performance compared to the Ascend 310. | ||

# | # Huawei claims 256 TFLOPs of FP16 performance for the Ascend 910. | ||

# | # The Tesla V100 has 112-125 TFLOPs for deep learning thanks to its tensor cores. | ||

2023年11月3日 (五) 14:12的版本

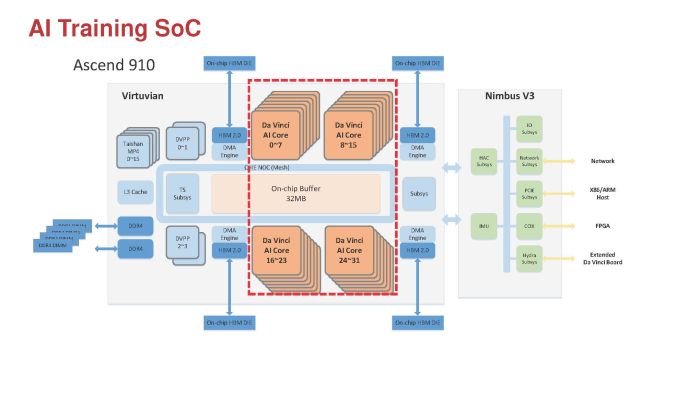

Architecture of Ascend 910 Chips

Main features:

- The Huawei Ascend 910 has 32 DaVinci AI cores.

- The chip combines these DaVinci AI cores with high-speed HBM2 memory.

- The main chip also has additional logic blocks such as 128 channel video decoding engines.

- There is a Nimbus V3 chip that handles most of the I/O and is co-packaged alongside the main chip and the HBM2 stacks.

- The Huawei Ascend 910 is designed to run at a higher power envelope (350W) and higher performance compared to the Ascend 310.

- Huawei claims 256 TFLOPs of FP16 performance for the Ascend 910.

- The Tesla V100 has 112-125 TFLOPs for deep learning thanks to its tensor cores.